# Modelling the Influence of Self-heating on Characteristics of IGBTs in the Sub-threshold Region

Krzysztof Górecki, and Paweł Górecki

Abstract—The paper refers to modelling characteristics of IGBT in SPICE software with self-heating taken into account. The form of the electrothermal model of the considered transistor and equations describing this model are proposed. The correctness of the proposed model is verified experimentally during the operation of the examined transistor at different cooling conditions. Particular attention is paid to the non-typical course of characteristics of the considered device at weak excitation. The shape of the obtained characteristics is discussed and the influence of the sub-threshold effect in the input MOS structure on these characteristics is analysed.

Index Terms—IGBT, electrothermal model, self-heating, SPICE

### I. INTRODUCTION

**P**OWER semiconductor devices are commonly used in switch-mode power supplies circuits and analogue electronic circuits operating in a continuous mode [1, 2, 3]. Within the range of high values of voltages and currents, IGBTs are practically used [2].

As it is commonly known, characteristics and technical parameters of semiconductor devices strongly depend on temperature [4, 5, 6]. As a result of thermal phenomena, among other things self-heating phenomena, the internal temperature  $T_j$  of semiconductor devices exceeds, sometimes considerably, the value of the ambient temperature  $T_a$ .

On the stage of designing electronic circuits, computer simulations are performed to verify correctness of the project. The reliability of the obtained results of calculations depends on the accuracy of the applied models [6, 7, 8, 9]. The highest accuracy characterizes the detailed models, but a high degree of their complication practically makes it impossible to use them in the analysis of networks containing a high number of semiconductor devices [5, 6, 7, 10]. Therefore, in the analysis of electronic networks, compact models of semiconductor devices describing dependences between voltages and currents on the connectors of these devices, are typically used.

More and more frequently in such analyses electrothermal compact models of the considered class of devices are used. Electrothermal models make it possible to calculate not only voltages and currents in the considered network, but also internal temperatures of the semiconductor devices. The collected electrothermal models have been formulated for many years for semiconductor devices [11 - 15].

K. Górecki and P. Górecki are with the Department of Marine Electronics, Gdynia Maritime University, Gdynia, Poland (e-mails: gorecki@am.gdynia.pl, pawel.gorka@wp.pl).

Due to widespread popularity of SPICE software, electrothermal models of semiconductor devices and integrated circuits dedicated for this software are important for designers of electronic circuits. Such models are proposed among others for power bipolar transistors in paper [12], for the power MOS transistor in [11], for the p-n diode in [16], or for monolithic integrated circuits dedicated for switch-mode power supplies in [15, 17, 18].

In this paper, which is an extended version of paper [19], the compact electrothermal model of IGBT for SPICE is proposed. In the second section the form of the worked out model is presented, and in the third section – the results of verification of its correctness are shown. Particularly, the influence of the sub-threshold effect on the dc characteristics of IGBTs is considered.

## II. MODEL FORM

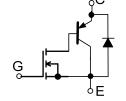

The structure of IGBT can be presented as the connection of the MOS transistor, the bipolar transistor and the p-n diode [20], shown in Fig. 1.

Fig. 1. The representation of the IGBT structure.

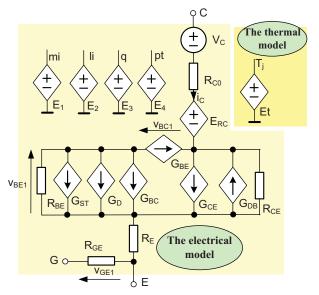

For the considered structure the electrothermal compact model dedicated for SPICE is formulated. Its network representation is shown in Fig. 2.

In the presented model two blocks can be distinguished: the electrical model and the thermal model. In the electrical model signals on the connectors G, C and E correspond to signals occurring on the connectors of the gate, the collector and the emitter of the real device. The device internal temperature is calculated in the thermal model and corresponds to the voltage in the node  $T_j$ . The value of this temperature is calculated using the following formula

$$T_{i} = T_{a} + R_{th} \cdot i_{C} \cdot v_{CE} \tag{1}$$

where  $R_{th}$  denotes thermal resistance of the investigated device,  $i_C$  is the collector current flowing through the voltage source  $V_C$  of the zero-value of the output voltage, while  $v_{CE}$  is the voltage between the connectors of the collector and the emitter. Series resistances of the emitter and the collector are modelled by means of linear resistors  $R_E$  and  $R_C$ . The linear dependence of series resistance on temperature models the controlled voltage source  $E_{RC}$ . Resistors  $R_{CE}$ ,  $R_{BE}$  and  $R_{GE}$  model leakages between the connectors of the transistor.

Fig. 2. The network representation of the compact electrothermal model of IGBT.

The drain current of the MOS transistor, existing in the structure of the considered IGBT, is equal to the sum of two components: the threshold current, modelled by the controlled current source  $G_{ST}$ , and the current of the MOS structure, represented by the controlled current source  $G_D$ . Currents of these sources are given by the formulas [11]

$$I_{GST} = I_{PO} \cdot \left(\frac{T_j}{T_0}\right) \cdot \exp\left(-\frac{U_{go}}{k/q} \cdot T_j\right) \cdot \left(\exp\left(\frac{LIMIT(v_{GE1} - v_{PH}, 0, v_{VT} - v_{PH})}{k/q} \cdot n_{ST} \cdot T_j\right) - 1\right) (2)$$

$$I_{GD} = \frac{v_{BE1}}{|v_{BE1}|} \cdot B \cdot v_{mi}$$

(3)

In equations (2), (3)  $I_{PO}$ ,  $n_{ST}$  and B are parameters of the transistor, whose values are estimated in the reference temperature  $T_0$ ,  $U_{go}$  is equal to 1.206 V for silicon, k means the Boltzmann constant and q is the electron charge. LIMIT is a standard-function of SPICE software. The voltages  $v_{BE1}$  and  $v_{GE1}$  are marked in Fig. 2. In turn,  $v_{PH}$  and  $v_{mi}$  denote voltages between the connectors of the controlled voltage sources  $E_4$  and  $E_1$ .

The controlled voltage sources  $E_1$ ,  $E_2$  are used for calculating values of the voltage  $v_{mi}$  according to the equations included in paper [11], whereas voltages on the controlled voltage sources  $E_3$  and  $E_4$  describe linear dependences of the threshold voltage and the Fermi's level on temperature.

The controlled current source  $G_{BE}$  describes the current flowing between the base and the emitter of the bipolar transistor included in the modelled structure. The current of this source is described by the dependence of the form

$$I_{GBE} = -\frac{I_O}{\beta_F} \cdot \left(\frac{T_j}{T_0}\right)^2 \cdot \exp\left(-\frac{U_{go}}{k_{q}' \cdot n_1 \cdot T_j}\right) \cdot \left(\exp\left(\frac{-v_{BC1}}{k_{q}' \cdot n_1 \cdot T_j}\right) - 1\right)$$

(4)

where  $I_0$  and  $n_1$  are parameters of the model, voltage  $v_{BC1}$  is marked in Fig. 2, while  $\beta_F$  is the current gain factor for the forward-active mode of the bipolar transistor and it is given by the formula [12]

$$\beta_F = \frac{\beta_{0F} \cdot \left(1 + a_F \cdot \left(T_j - T_0\right)\right)}{1 + b_F \cdot \left(1 + c_F \cdot \left(T_j - T_0\right)\right) \cdot |i_c|} \cdot \left[1 - \sum_i \gamma_{iF} \cdot \exp\left(-\alpha_{iF} \cdot |i_c|\right)\right]$$

(5)

where  $a_F$ ,  $b_F$ ,  $c_F$ ,  $\gamma_{iF}$ ,  $\alpha_{iF}$ ,  $\beta_{OF}$  denote the model parameters in the forward active mode.

In turn, the controlled current source  $G_{BC}$  represents the current flowing between the base and the collector of the bipolar transistor included in the modelled structure. The current of its source is described by

$$U_{GBE} = -\frac{I_o}{\beta_R} \cdot \left(\frac{T_j}{T_0}\right)^2 \cdot \exp\left(-\frac{U_{go}}{k/q} \cdot n_1 \cdot T_j\right) \cdot \left(\exp\left(\frac{-v_{BE1}}{k/q} \cdot n_1 \cdot T_j\right) - 1\right) (6)$$

where the voltage  $v_{BE1}$  is marked in Fig. 2,  $\beta_R$  is the current gain factor for the reverse-active mode of the bipolar transistor and it is given by

$$\beta_R = \beta_{0R} \cdot \left( 1 + a_F \cdot \left( T_j - T_0 \right) \right) \tag{7}$$

In equation (7)  $\beta_{OR}$  is equal to the value of the current gain factor for the reverse-active mode at the reference temperature  $T_0$ .

The main current of IGBT is modelled by the controlled current source  $G_{CE}$  described by

$$I_{GCE} = I_{O} \cdot \left(\frac{T_{j}}{T_{0}}\right)^{2} \cdot \exp\left(-\frac{U_{go}}{k/q} \cdot n_{1} \cdot T_{j}\right) \cdot \left(1 + \frac{v_{CE}}{V_{AN}}\right)$$

$$\cdot \left(\exp\left(\frac{-v_{BC1}}{k/q} \cdot n_{1} \cdot T_{j}\right) - \exp\left(\frac{-v_{BE1}}{k/q} \cdot n_{1} \cdot T_{j}\right)\right)$$

(8)

where V<sub>AN</sub> denotes Early's voltage.

The dc characteristic of the reverse diode describes the controlled current source  $G_{DB}$ . The current of this source is given by the following formula

$$I_{GDB} = I_{OD} \cdot \left(\frac{T_j}{T_0}\right)^2 \cdot \exp\left(-\frac{U_{go}}{k/q} \cdot n_D \cdot T_j\right) \cdot \left(\exp\left(\frac{-v_{CE1}}{k/q} \cdot n_D \cdot T_j\right) - 1\right) + (9)$$

$$+ I_{OG} \cdot \left(\frac{T_j}{T_0}\right) \cdot \exp\left(-\frac{U_{go}}{k/q} \cdot n_{D1} \cdot T_j\right) \cdot \left(\exp\left(\frac{-v_{CE1}}{k/q} \cdot n_{D1} \cdot T_j\right) - 1\right)$$

where  $I_{\text{OD}},\ I_{\text{OG}},\ n_{\text{D}}$  and  $n_{\text{D1}}$  are parameters of the presented model.

# **III. RESULTS**

To verify the correctness of the model described in the second section, dc characteristics of the arbitrarily selected IGBT of the type IRG4PC40UD by International Rectifier are measured and calculated. This transistor is characterized with the admissible value of the reverse voltage  $V_{CEmax} = 600$  V, with the admissible value of the collector current  $I_{Cmax} = 20$  A and with the admissible value of dissipated power  $P_{tot} = 65$  W [21].

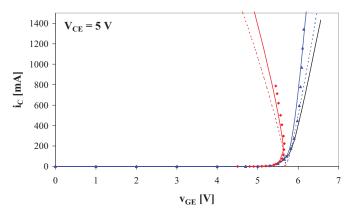

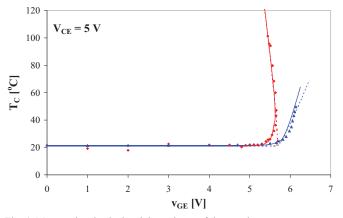

In Figs. 3 - 11 the results of calculations and measurements of dc characteristics of the considered transistor obtained at different cooling conditions are collected. The values of parameters of the electrothermal model of IGBT used in the calculations are collected in Table I.

TABLE I. PARAMETERS VALUES OF THE ELECTROTHERMAL MODEL OF THE TRANSISTOR IRG4PC40UD

|           | X7 FX71             | rrz-la                            | $D \Gamma A / V^2 I$        | T [17]                 | 0. 17 7-12          |

|-----------|---------------------|-----------------------------------|-----------------------------|------------------------|---------------------|

| parameter | V <sub>T0</sub> [V] | $\alpha_{\rm T} [\rm K^{-1}]$     | $B[A/V^2]$                  | T <sub>0</sub> [K]     | $\lambda [V^{-1}]$  |

| value     | 5.62                | $1.4 \times 10^{-3}$              | 0.1                         | 300                    | $2x10^{-3}$         |

| parameter | $PH_0[V]$           | $\alpha_{\rm PH}  [{\rm K}^{-1}]$ | I <sub>0</sub> [A]          | $n_1$                  | $\beta_{OF}$        |

| value     | 0.85                | $3x10^{-3}$                       | $10^{3}$                    | 1.4                    | 65                  |

| parameter | $\beta_{OF}$        | $a_{\rm F} [{\rm K}^{-1}]$        | $c_{\rm F}  [{\rm K}^{-1}]$ | $b_{\rm F} [A^{-1}]$   | V <sub>AN</sub> [V] |

| value     | 3                   | 6x10 <sup>-3</sup>                | $2x10^{-3}$                 | 3                      | 1000                |

| parameter | I <sub>P0</sub> [A] | n <sub>P</sub>                    | I <sub>0D</sub> [A]         | n <sub>D</sub>         | I <sub>0G</sub> [A] |

| value     | $4x10^{3}$          | 5.8                               | 500                         | 1.5                    | 5                   |

| parameter | n <sub>D1</sub>     | $R_{C}[\Omega]$                   | $R_{E}[\Omega]$             | $\alpha_{RC} [K^{-1}]$ |                     |

| value     | 5                   | 0.35                              | 0.1                         | 3x10 <sup>-3</sup>     |                     |

The value of thermal resistance  $R_{th}$  depends on cooling conditions of the transistor. Isothermal characteristics obtained at ideal cooling conditions are calculated for  $R_{th} = 0$ . Additionally, non-isothermal characteristics of the considered transistor operating without the heat-sink ( $R_{th} = 35$  K/W) and the transistor situated on the aluminium heat-sink ( $R_{th} = 6.5$  K/W) are calculated. The values of  $R_{th}$  are measured with the use of the method described in the paper [22].

In the figures included in the further part of this section, black dashed lines mean the results of isothermal calculations, blue solid lines - the results of electrothermal calculations for the transistor situated on the heat-sink, red solid lines - the results of electrothermal calculations for the transistor operating without the heat-sink, and points - the results of measurements. In order to illustrate the influence of taking into account the sub-threshold phenomena in the MOS input structure, in all the figures dashed red and blue lines denote the results of calculations obtained omitting this phenomena. The current-voltage characteristics are measured by means of the source meter Keithley 2612, and the case temperature of the transistor is measured by means of the thermo-hunter PT-3S by Optex. The calculated values of the case temperature are obtained on the ground values of the internal temperature with the use of the formula from paper [23].

In Fig. 3 the calculated and measured transfer characteristics of the examined transistor obtained at the voltage between the collector and the emitter  $V_{CE} = 5$  V are presented, whereas in Fig. 4 - corresponding to them dependences of the case temperature of the transistor on the control voltage  $v_{GE}$ .

Fig. 3. Measured and calculated transfer characteristics of the investigated transistor at  $V_{CE}$  = 5 V.

As it can be noticed, the threshold voltage of the examined transistor exceeds 5.5 V. Together with worsening its cooling conditions the considered characteristic  $i_C(v_{GE})$  moves left. It is worth paying attention to the calculated and measured characteristics of the transistor operating without any heat-sink, which for the current  $i_C > 100$  mA show the negative slope. Omitting the sub-threshold part of the current of the input MOS structure results in understating the value of the collector current. It is very visible in the range of small values of the current  $i_C$ . In this case, the device case temperature  $T_C$  rises to  $100^{\circ}$ C, whereas for the transistor situated on the heat-sink - to  $50^{\circ}$ C.

Fig. 4. Measured and calculated dependence of the transistor case temperature on the voltage  $v_{\text{GE}}$

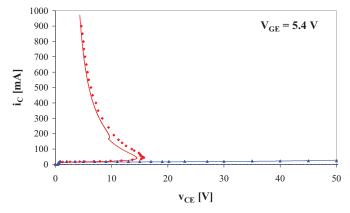

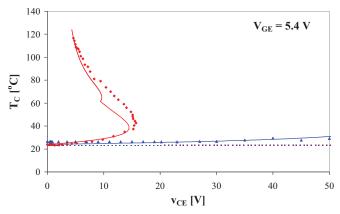

Fig. 5 presents the output characteristics of the considered transistor obtained at the voltage  $V_{GE} = 5.4$  V, lower than the threshold voltage, whereas Fig. 6 - corresponding to them dependences of the device case temperature on the voltage  $V_{CE}$ .

In the case of ideal cooling and for the transistor situated on the heat-sink the collector current has low values, resulting from the operation of the input MOS transistor in the subthreshold range. For the transistor operating without any heatsink the case temperature rise of this device equal to  $18^{\circ}$ C causes only a sharp increase of the collector current and a decrease of the voltage v<sub>CE</sub>. In this range, the input MOS transistor passes from the sub-threshold range to the saturation range. The case temperature of the transistor goes up to  $120^{\circ}$ C and the value of the threshold voltage decreases under the value of the control voltage V<sub>GE</sub>. When the sub-threshold phenomena is omitted, the transistor operates in the cut-off range and the i<sub>C</sub> current is nearly zero, whereas the device case temperature is equal to the ambient temperature.

Fig. 5. Measured and calculated output characteristics of the investigated transistor at  $V_{GE}$  = 5.4 V.

Fig. 6. Measured and calculated dependence of the transistor case temperature on the voltage  $v_{CE}$  at  $V_{GE} = 5.4$  V.

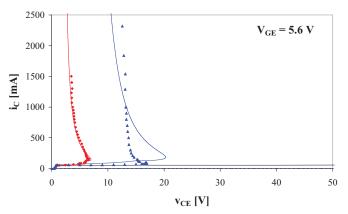

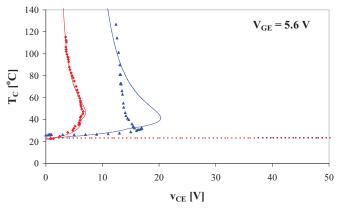

Fig. 7 presents the output characteristics of the examined transistor obtained at the voltage  $V_{GE} = 5.6$  V, lower by only just 20 mV from the threshold voltage, whereas Fig. 8 - corresponding to them dependences of the device case temperature on the voltage  $v_{CE}$ .

As it can be noticed, both for the transistor situated on the heat-sink and for the transistor operating without any heatsink, there appear sections of the negative slope. The change of the sign of the slope of these characteristics appears when the case temperature of the device exceeds  $40^{\circ}$ C. Unfortunately, at the considered value of the voltage v<sub>GE</sub>, only qualitative agreement between the calculated and measured characteristics for the transistor situated on the heat-sink is obtained. For the model without the sub-threshold phenomena, the collector current is near zero and the case temperature is practically equal to the ambient temperature.

Fig. 7. Measured and calculated output characteristics of the investigated transistor at  $V_{GE}\,{=}\,5.6$  V.

Fig. 8. Measured and calculated dependence of the transistor case temperature on the voltage  $v_{CE}$  at  $V_{GE}$  = 5.6 V.

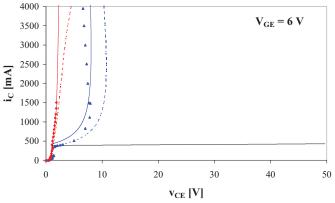

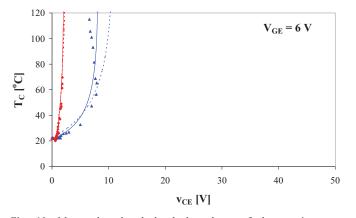

Figs. 9 and 10 illustrate the output characteristics of the considered transistor and the dependence  $T_C(v_{CE})$  at the voltage  $V_{GE} = 6$  V. It is clearly visible that worsening the cooling conditions of the transistor causes an increase in the value of the collector current  $i_C$  at the fixed value of the voltage  $v_{CE}$ . In this case, the output characteristics have a positive slope in the whole examined range of voltages and currents.

Fig. 9. Measured and calculated output characteristics of the investigated transistor at  $V_{\text{GE}}$  = 6 V.

Fig. 10. Measured and calculated dependence of the transistor case temperature on the voltage  $v_{CE}$  at  $V_{GE} = 6$  V.

For the transistor operating without any heat-sink the influence of the sub-threshold effect on the considered characteristics is not visible, whereas for the transistor situated on the heat-sink one can observe that the considered characteristics move to the right direction when the subthreshold effect is not taken into account.

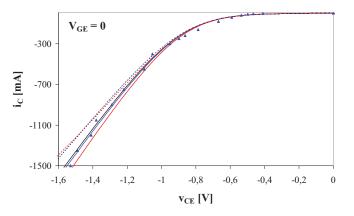

Fig. 11. Measured and calculated reverse output characteristics of the investigated transistor at  $V_{\text{GE}}\,{=}\,0.$

The output characteristic in reverse polarization of the examined transistor is shown in Fig. 11. This characteristic practically does not change the course for all the considered cooling conditions of the examined device. Series resistance of the transistor has essential influence on the course of the considered characteristic.

## **IV. CONCLUSIONS**

In this paper, the electrothermal model of IGBT dedicated for SPICE is proposed. This model has a simple form, and, nonetheless, makes possible the correct calculation of nonisothermal characteristics of the considered device at different cooling conditions. Except terminal voltages and currents the proposed model makes it also possible to calculate the internal temperature and the case temperature of the examined device.

The presented results of calculations and measurements show that, as a result of self-heating phenomena, changes in the shape of characteristics of the considered device are visible. Particularly, the negative slope of the non-isothermal transfer and output characteristics of the considered transistor while exciting this device with the voltage of the value not strider than the threshold voltage, is observed. This phenomenon results from the high value of the sub-threshold component of the drain current of the MOS structure existing in the analysed IGBT, being an exponentially increasing function of the internal temperature of the transistor, and the decreasing dependence of the threshold voltage on this temperature.

It is worth noticing, that the sub-threshold phenomenon, typically omitted in classical IGBT models [24] is very important, when the considered device operates with low control signal. In this situation, the output characteristics of the IGBT can have a shape of the letter S and the collector current can attain values even some thousands higher than the values obtained without sub-threshold phenomena taken into account.

#### REFERENCES

- Ericson R., Maksimovic D., Fundamentals of Power Electronics, Norwell, Kluwer Academic Publisher, 2001.

- [2] Rashid M.H., Power Electronic Handbook. Academic Press, Elsevier, 2007.

- [3] Kazimierczuk M.K., Pulse-width Modulated DC-DC Power Converters. John Wiley &Sons, Ltd, 2008

- [4] Singh J., Semiconductor Devices. Basic Principles. John Wiley & Sons, 2001.

- [5] Janke W., Zjawiska termiczne w elementach i układach półprzewodnikowych, WNT, Warszawa 1992

- [6] Zarębski J., Tranzystory MOS mocy, Fundacja Rozwoju Akademii Morskiej w Gdyni, Gdynia 2007

- [7] Górecki K., Zarębski J., Influence of MOSFET Model Form on Characteristics of the Boost Converter. Informacije MIDEM, Vol. 41, No. 1, 2011, pp. 1-7.

- [8] Maksimovic D., Stankovic A.M., Thottuvelil V.J., Verghese G.C., Modeling and simulation of power electronic converters, Proceedings of the IEEE, Vol. 89, No. 6, 2001, pp. 898-912.

- [9] Mohan N., Robbins W.P., Undeland T.M., Nilssen R., Mo O., Simulation of Power Electronic and Motion Control Systems – An Overview, Proceedings of the IEEE, Vol. 82, 1994, pp. 1287-1302.

- [10] Rashid M., Rashid H., SPICE for Power Electronics and Electronic Power, Taylor and Francis Group, LCC, EngNetBase

- [11] Zarębski J., Górecki K., The electrothermal large-signal model of power MOS transistors for SPICE. IEEE Transaction on Power Electronics, Vol. 25, No. 5-6, 2010, pp. 1265 – 1274.

- [12] Zarębski J., Górecki K., SPICE-aided modelling of dc characteristics of power bipolar transistors with selfheating taken into account. International Journal of Numerical Modelling Electronic Networks, Devices and Fields, Vol. 22, No. 6, 2009, pp. 422-433.

- [13] Mawby P.A., Igic P.M., Towers M.S., Physically based compact device models for circuit modelling applications, Microelectronics Journal, Vol. 32, 2001, pp. 433-447.

- [14] Starzak, Ł., Zubert, M., Janicki, M., Torzewicz, T., Napieralska, M., Jabloński, G., Napieralski, A., Behavioral approach to SiC MPS diode electrothermal model generation. IEEE Transactions on Electron Devices, Vol. 60, No. 2, 2013, pp. 630-638

- [15] Górecki K., The electrothermal macromodel of switching voltage regulators from L4970 family. International Journal of Numerical Modelling Electronic Networks, Devices and Fields, Vol. 21, No. 6, 2008, pp. 455-473.

- [16] Górecki K., Zarębski J., Modeling Nonisothermal Characteristics of Switch-Mode Voltage Regulators. IEEE Transactions on Power Electronics, Vol. 23, No. 4, 2008, pp. 1848 – 1858.

- [17] Zarębski J., Górecki K., SPICE-Aided Modelling of the UC3842 Current Mode PWM Controller with Selfheating Taken into Account. Microelectronics Reliability, Vol. 47, No. 7, 2007, pp. 1145-1152.

- [18] Zarębski J., Górecki K., Electrothermal Compact Macromodel of Monolithic Switching Voltage Regulator MC34063A. Microelectronics Reliability, Vol. 48, No. 10, 2008, pp. 1703-1710.

- [19] Górecki K., Górecki P., Modelling the influence of self-heating on characteristics of IGBTs. Proceedings of the 21<sup>st</sup> International Conference Mixed Design of Integrated Circuits and Systems MIXDES, 2014, Lublin, pp. 298-302.

- [20] Napieralski A., Napieralska M., Polowe półprzewodnikowe przyrządy dużej mocy. Wydaw. Naukowo-Techniczne, Warszawa, 1995.

- [21] IRG4PC40UD Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery Diode, Data sheet, International Rectifier, 1997

- [22] Górecki K., Górecki P., The DC measurement method of thermal resistance of IGBTs. Proceedings of the 20<sup>th</sup> International Conference Mixed Design of Integrated Circuits and Systems MIXDES 2013, Gdynia, pp. 333-337

- [23] Zarębski J., Górecki K., Modelling CoolMOS Transistors in SPICE. IEE Proceedings on Cicuits, Devices and Systems, Vol. 153, No. 1, 2006, pp. 46-52.

- [24] A.R.Hefner, Jr., An Investigation of the Drive Circuit Requirements for the Power Insulated Gate Bipolar Transistor (IGBT), IEEE Transactions on Power Electronics, Vol. 6, No. 2, April 1991, pp. 208-219.

**Krzysztof Górecki** (M'05 – SM'06) was received the M.Sc. and Ph.D. degrees in electronics from the Technical University of Gdańsk, Gdańsk, Poland, in 1990 and 1999, respectively and the D.Sc. degree from Technical University of Łódź, Łódź, Poland, in 2008. He is an Associate Professor with the Department of Marine Electronics, Gdynia Maritime University, Gdynia, Poland. His research interests are in the areas of modelling, analysis and measurements of semiconductor devices and electronic circuits, particularly including thermal effects.

**Paweł Górecki** is a student of the Faculty of Electrical Engineering in Gdynia Maritime University, Gdynia, Poland. His research interests are in the areas of power semiconductor devices and photovoltaic systems.