# Trapezoidal Waveform Generator with Voltage-range and Slew-rate Control Ability

### Mariusz Jankowski

Abstract—The paper introduces an analog circuit designed as a provider of a trapezoidal waveform, scalable in amplitude and slew-rate value. In addition the circuitry is equipped with edgerounding capability, implemented inside output voltage buffer. Schematics, rule of operation and exemplary simulations are included.

Index Terms—Trapezoidal waveform generator, voltage discriminator, slew-rate control, edge rounding.

# I. INTRODUCTION

ANALOG signal generation is, as a rule, a complex task, depending on analog system requirements. Process of signal forming generally is a multi-step operation due to specific features of the generated signal. On the other hand, complicated multi-stage circuitry imprints its own non-idealities into the resulting final waveform.

Thus, it would be reasonable to reduce number of signal processing stages, e.g. by making them multi-purpose ones. One such solution is described in this paper. The circuit presented here generates trapezoidal voltage signal with adjustable slew-rate and voltage-range. Signals of that sort are used e.g. in wireless transmission systems, including automotive solutions. Signal rounding enables avoiding of high frequency noise at the moments of large slew-rate value changes of transmitted signals. Such occurrence may violate transmission and EMC rules and eliminate circuit from market.

# II. OVERVIEW OF A CIRCUIT

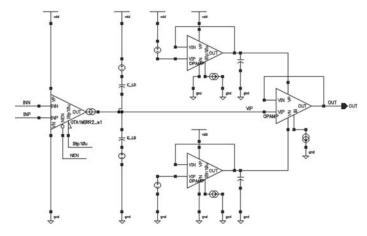

The introduced circuit consists of two main blocks. The first one produces trapezoidal constant slew-rate waveform ranging from ground to supply voltage.

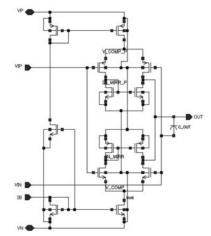

The second stage works as: a buffer for current-mode output of the preceding stage, an output signal voltage-range limiter and edge-rounder. Fig. 1 presents general view of the circuit structure, with additional OPAMPs providing sources of virtual ground and supply voltages.

### III. GENERATION OF TRAPEZOIDAL WAVEFORMS

Trapezoidal waveform generation used in the circuitry is based on principle of consecutive charging and discharging of capacitor with constant currents. Such operation can be performed by various circuits [1]. The commonly used

M. Jankowski is with the Department of Microelectronics and Computer Science, Technical University of Lodz, ul. Wolczanska 221/223, B18, 90-924 Lodz, POLAND; e-mail: jankowsk@dmcs.p.lodz.pl.

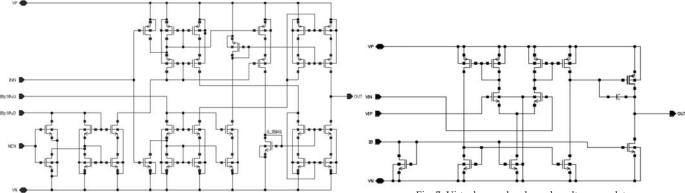

structure is the output stage consisting of complementary current mirrors and load capacitors.

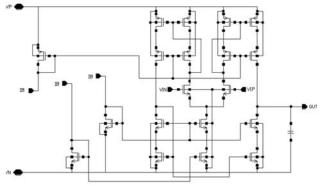

Exemplary solution is shown in paper [2]. It is a kind of modified OTA circuit [4], depicted in Figure 2. It has two types of bias current inputs – one for circuitry biasing and other for slew-rate value setting. In fact, this circuit has two slew-rate coding currents – for rising and falling signal edge as well as additional current injection point (Fig. 3), driven from the following block of edge-rounding process control, presented in Figure 4. The edge-control block controls voltage of the generated waveform and when this voltage approaches one of defined voltage-limits, it starts subtracting capacitor charging /discharging current from the output mirror stage of the waveform generator presented in Figure 3, so as to stop waveform voltage change just when it equals the defined voltage limit. The OPAMPs present in Figure 4 can usually be quite simple structures, like one included in Figure 7.

Fig. 1. Current-controlled waveform generator.

Fig. 2. Modified OTA working as capacitor-driving circuitry.

Fig. 3. Modified OTA used in circuit presented in [2].

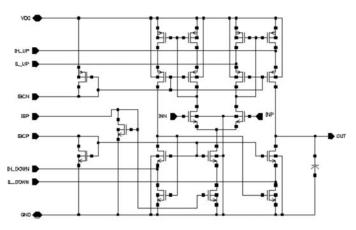

In the solution described in this paper a similar solution is applied. The one difference is that the new generation stage utilizes current-flow bypassing switches, which do not force current-flow stop during switching process, but just changes its route, additionally switching down inputs of related mirror inputs (Fig. 5). Such approach stabilizes the circuitry power consumption.

Other difference is application of a quite straightforward structure for voltage-limit and edge-rounding control purpose, instead of rather complex structure mentioned above.

The stability of slew-rate value of the output signal depends on output impedance of current mirrors that form the output stage, as well as on quality of capacitors available in utilized technological process. In presented circuitry, cascode mirrors are used. If higher quality of output waveform is required, regulated-cascode circuits can be used.

## IV. EDGE-ROUNDING AND VOLTAGE-RANGE DEFINITION

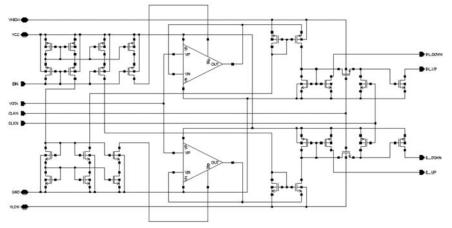

The signal rounding and voltage-range limiting procedures are both performed by one signal-processing stage. The stage is a direct concatenation of two simple OPAMPs, one equipped with NMOS differential pair and one with PMOS differential pair. These OPAMPs are connected at input and output terminals.

These OPAMPs form a kind of simple pseudo rail-to-rail OPAMP (Fig. 6), which is used as a simple non-inverting buffer. Another modification is power connection of this double OPAMP to two voltage regulators, which provide virtual supply and ground voltages equal to limits imposed on the output voltage.

The virtual supply and ground providers can be produces by quite simple OPAMP structures. Simple OPAMP solution presented in [3] and shown in Fig. 7, is enough for supplying the concatenated OPAMP due to its low power consumption level. Also simpler specialized solutions can be used, because full voltage-range operation of these OPAMP voltage-regulators is not required in presented circuitry.

Fig. 4. Voltage-limit and edge-rounding control block used in [2].

Fig. 6. Simple pseudo rail-to-rail OPAMP.

Fig. 5. Trapezoidal signal generation circuitry.

Fig. 7. Virtual ground and supply voltage-regulator.

The voltage-limiting effect in the presented OPAMP is due to fact, that its input is driven with signal that over- and undershoots levels of, respectively, virtual supply and ground voltage. The input signal cannot consequently pass supply voltage levels of the concatenated OPAMP and finally output signal stops following the input signal and remains stable at virtual supply and ground levels.

Signal voltage rounding effect is produced because if input voltage approaches one of virtual power levels, one of simple OPAMPs gradually switches itself off, due to extinguishing of the current source that biases OPAMP's differential pair. The output signal distraction effect is extended by over- and undershoots of input voltage over/under related power voltage. If these input voltage level excesses are large enough, more and more distorted output signal reaches level of virtual ground or virtual supply. The rounding effect is in fact a side effect of non-ideal operation of simple OPAMPs inside the concatenated OPAMP.

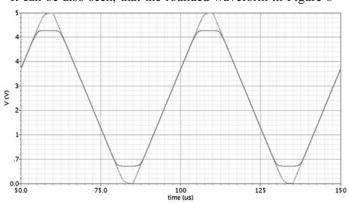

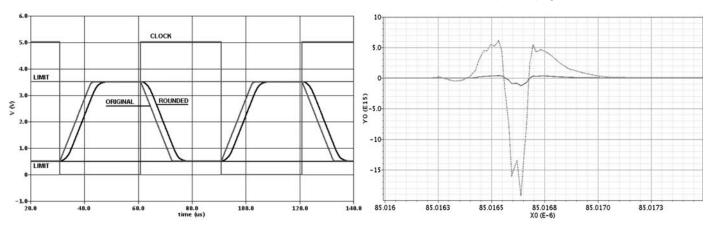

Time domain simulation results are presented in Fig. 8. Output signals of both consecutive signal generation stages are shown. The required rounding and voltage-range limiting functionality can be observed. It can be seen that the original trapezoidal waveform also gets rounded but only when it approaches its maximum of minimum voltage level. When it leaves its extreme voltage levels, no edge-rounding happens.

It can be also seen, that the rounded waveform in Figure 8

Fig. 8. Original (dotted line) and rounded (solid line) signal of the circuit.

is free from phenomenon present in output waveform of circuit explained in [2, 3]. Figure 9 shows phase-shift between original and rounded waveforms, that can be clearly observed in solution presented in [2]. It is inevitable by-product of the very way of voltage-limit and edge-rounding circuitry operation.

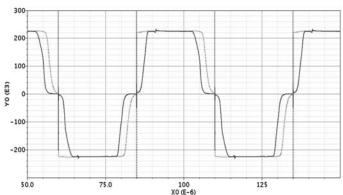

Fig. 10 shows first derivatives of the trapezoidal and rounded signal. It can be seen that slew-rate value of the rounded signal is slightly deteriorated. This phenomenon is related to fact that during operation of the concatenated OPAMP, its inside OPAMPs go off and on consecutively, according to input voltage level, and this in turn influences the operating sub-OPAMP of the circuit. For number of applications such signal behavior is acceptable, because it does not produce high frequency harmonics in rounded output waveforms.

Critical regions of the original signal and their absence in the rounded signal can be observed in Fig. 11. It shows second derivatives of voltage signals

High value of second derivative marks time-points where high frequency harmonics appear in the voltage signals. It can be observed that maximum value of original signal second derivatives 15-20 time exceeds values observed in rounded signal. Significant improvement in signal quality, understood as absence of high frequency incursions, can be observed in the rounded output waveform.

Fig. 10. Derivatives of original (dotted line) and rounded (solid line) signal of the circuit.

Fig. 9. Original and rounded signal of the circuit in [2].

Fig. 11. Close-in view of derivatives of original (dotted line) and rounded (solid line) signals of the circuit.

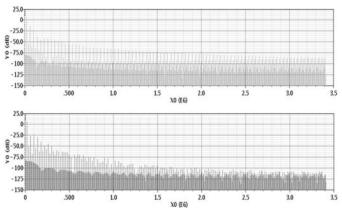

More precise comparison of both signals is made my means of Discreet Fourier Transform (Fig. 12). The figure shows level of harmonics for the rounded waveform being lower than in case of original waveform. Such operation improvement may be crucial for meeting EMC norms and regulations in circuits incorporated into integrated systems to be introduced to market sale.

Fig. 12. DFTs of original (upper) and rounded (lower) generator signals.

Mariusz Jankowski (received the M.Sc. and Ph.D. degrees in electronics engineering from the Technical university of Lodz, Lodz, Poland, in 1998 and 2003, respectively.

He is an Assistant Professor with the Department of Microelectronics and Computer Science at Technical University of Lodz, Poland. His research interests include analysis and design of mixed signal integrated circuits, including high-voltage applications, design of integrated 3D circuits, at

present he works on 3D circuits and EMC issues. He is the author or coauthor of more than 30 publications, including two chapters in books.

### V. CONCLUSION

The presented circuit shows simple but efficient way of providing limited voltage-range, regulated slew-rate, trapezoidal waveform generator, equipped with signal rounding ability.

Structure of the proposed circuit consists of only two modules due to making them a multi-role blocks. Such a short signal-processing path is an efficient way of avoiding signal distortion that takes place during elaborate signal processing in waveform generators designed as long series-connected chains of processing subcircuits.

### REFERENCES

- United States Patent 5025172, "Clock generator generating trapezoidal waveform," Issued on June 18, 1991.

- [2] M. Jankowski, "Adjustable Output Voltage-Range Trapezoidal Waveform Generator with Harmonics-Reduction Functionality," International Conference TCSET'2008, Lviv-Slavsko, Ukraine, February, 19-23, 2008.

- [3] M. Jankowski, "Trapezoidal Waveform Generation Circuit with Adjustable Output Voltage Range," International Conference CADSM'2007, Polyana, Ukraine, February, 20-24, 2007.

- [4] R. J. Baker, "Cmos: Circuit Design, Layout, and Simulatiofn, 2nd Edition", Wiley-IEEE Press, November 2004.